Hello Dear Readers,

Today, I will explain how to design a Layout in the MAGIC layout tool and how to perform SPICE simulation.

CMOS inverters (Complementary NMOSFET Inverters) are some of the most widely used and adaptable MOSFET inverters used in chip design. They operate with very little power loss and at relatively high speed. Furthermore, the CMOS inverter has good logic buffer characteristics, in that, its noise margins in both low and high states are large.

A CMOS inverter containing a PMOS and an NMOS transistor connected at the drain and gate terminals, a supply voltage VDD at the PMOS source terminal, and a ground connection at the NMOS source terminal Vin is connected to the gate terminals, and Vout is connected to the drain terminals As shown in Fig.1 is a circuit-level symbol but in the layout-wise internal structure of CMOS is consisted of common P-Type Substrate for building NMOS and N-Well implanted for building PMOS as shown in Fig.2.

|

| Fig.1 CMOS Inverter |

|

| Fig.2 CMOS Inverter Internal Structure |

|

| Fig.3 Magic Layout initial screen |

|

| Fig.4 N-well And p-type diffusion overlap |

After that now we want to draw a polysilicon layer to build the gate terminal of PMOS. After that metal-1 and substrate contacts layer formed to build complete PMOS as shown in Fig.5. Similarly, we build NMOS and shorted Polysilicon of PMOS and NMOS together to the formed input terminal of the Inverter and shorted the drain layer to the formed output terminal as shown in Fig.6. After that we have to provide labels of VDD, gnd, in, and out as shown in the final layout.

|

| Fig.6 CMOS Inverter final layout |

So after the final layout save the layout go to the command line screen of the magic and type first "extract all" and then "ext2spice" as shown in Fig.7. Now go to path in which layout is saved so we found the .spice format file and .mag format file. So copy the .spice file and make a new directory on which paste it and then go to the PTM model and copy the entire web page and make the text file in the same directory on which the spice file was saved. Now open spice file and do some changes such as include model file, apply the supply voltage and input pulse signal for functional verification as shown in Fig.8.

|

| Fig.7 Extract Layout |

|

| Fig.8 Updated SPICE file |

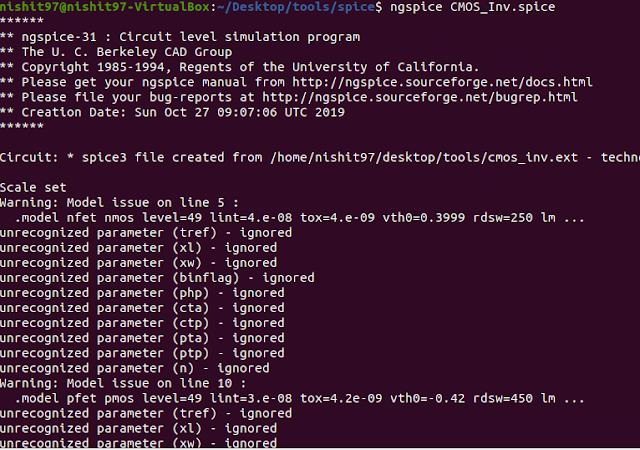

Now open the terminal from this directory and open Ngspice with spice file as shown in Fig.9 and type command "run" first and then type "plot in out". The simulational waveform is shown in Fig.10.

Spoken Tutorial found Here.

Wow first time all doubts regarding Magic plus Ngspice is solved.thanks for your effort

ReplyDeleteOne of the blog in which I found this much easy explanation and project wise learning. Bro keep it up and never stop this work.

ReplyDeleteFantastic learning based post.

ReplyDeleteYou are a next level motivation person. Really in india I never find other blog such user friendly.

ReplyDeleteYou are really slow learner, I really like your content accuracy specifically verilog code is always bugs free. So best wish and keep it up

ReplyDeleteAmazing! Accurate and very well explained.

ReplyDeleteThis comment has been removed by a blog administrator.

ReplyDeleteReally helpful for beginners

ReplyDeleteSo simple and solved all the query regarding extraction and spice simulation. Thanks dear for your effort 😶😶😶😶

ReplyDeleteOne of the excellent post regarding layout verification through spice simulation. I read your post regularly and big fan of you 👍👍and I am a professor at IITH.

ReplyDeleteIt's my motivation thanks sir for your feedback and appreciation. I will do my best forever.

DeleteOne of superb article

ReplyDeleteSuperb post I really like the way of the contents and simpler explanation.

ReplyDelete