Hello Dear Readers, Today in this post, I will provide some deep insight into the Signal Electromigration (Signal EM): Violations, Examples, and Practical Fixes. 1. Introduction: As technology nodes shrink into the deep‑submicron and nanometer regime (7nm, 5nm, 3nm and beyond), electromigration (EM) has become a first‑order reliability concern—not only for power/ground (PG) networks but also for signal nets. Signal EM failures are often underestimated because signal currents are transient and bidirectional. However, with higher switching activity, tighter metal pitches, thinner wires, and aggressive timing closure, signal EM can cause latent or early‑life failures if not addressed properly. This article explains: What Signal EM is and how it differs from PG EM Typical Signal EM violation scenarios Detailed, practical examples Root causes behind each violation Proven solutions and best practices to fix and prevent Signal EM issues 2. What is Signal Electromigration: El...

Hello Dear Readers,

Today I have designed this page for doing exercises regarding STA-related Questions.

Q-1:

The circuit in Fig. 1. is the internal layout of a custom-built chip. The tpd for each gate is listed below it. The delays for the register are all the same and listed in the lower right corner. What is the Maximum Clock Frequency of the below gate-level netlist?

|

| Fig. 1 |

Q-2:

Here I will upload more as I will come across any good questions. Thanks for reading

Connect with me

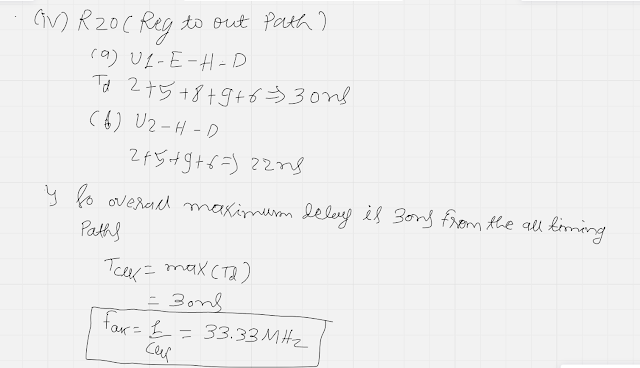

For each of the following circuits:

(i). Calculate the worst-case pin-to-pin combinational delay, clock-to-output delay, and register-to-register delay.

(ii). Use this data to find the maximum clock frequency.

(iii). Calculate tsu and thd for the external inputs.

Q-3: Are Setup and Hold times of the flip-flop is intrinsic parameters or design parameters.

Q-4: Setup and Hold times of the flip-flop are controllable or not, explain your answer.

Incredible your posts but if you will provide answer then it will be helpful. Please keep it up

ReplyDeletenow uploaded

Deletewhere ?

DeleteYes bro please upload answer also will be more beneficial for us. I hope you will consider it and work on it. Best wishes.

ReplyDeleteyes, uploaded now

Deletethanks bro long waiting keeps it up

DeleteAmazing posts you are always come with more excitements hope you will also coming with answers.

ReplyDeleteQuestions are so much good level but please provide solution also will be helpful to us.

ReplyDelete